Простейшие схемы

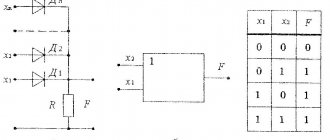

Первая схема представляет собой простейший пробник

для прозвонки электрических цепей. С помощью данного пробника можно определить надёжность электрического контакта, найти обрыв в цепи, проверить исправность резисторов и полупроводниковых диодов и транзисторов.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Схема пробника для прозвонки электрической цепи.

Опишем его работу. При разомкнутых щупах ХТ на входах логического элемента DD1 относительно общего провода устанавливается высокий логический уровень напряжения. Соответственно на выходе элемента DD1 будет низкий логический уровень, при этом светодиод VD1 не будет гореть. Если щупы замкнуть между собой, то на входе DD1 будет низкий логический уровень, а на выходе – высокий. Светящийся диод сообщит о том, что выходы замкнуты между собой. Таким образом, при подключении щупов к исправной цепи будет загораться светодиод, а если светодиод не горит – значит, в цепи имеется обрыв.

Следующая схема, представленная ниже, представляет собой логический пробник

. Предназначенный он для определения логического уровня напряжения в электрических цепях цифровых устройств.

Схема логического пробника.

В исходном состоянии на входах логического элемента DD1 и выходе DD2 устанавливается высокий логический уровень, соответственно светодиод VD1 горит. При включении светодиодов в цепь с высоким логическим уровнем светодиод VD1 продолжает гореть, а когда на входе DD1 появится низкий логический уровень, то светодиод VD1 соответственно погаснет.

Дальнейшее повествование о применении цифровых микросхем не возможно без знания внутреннего устройства

цифровых ТТЛ и КМОП микросхем и их

передаточных характеристиках

.

Что такое интегральная микросхема

Интегральная микросхема — это миниатюрный электронный блок, содержащий в общем корпусе транзисторы, диоды, резисторы и другие активные и пассивные-элементы, число которых может достигать нескольких десятков тысяч.

Одна микросхема Может заменить целый блок радиоприемника, электронной вычислительной машины (ЭВМ) и электронного автомата. «Механизм» наручных электронных часов, например, — это всего лишь одна большей микросхема.

По своему функциональному назначению интегральные микросхемы делятся на две основные группы: аналоговые, или линейно-импульсные, и логические, или цифровые, микросхемы.

Аналоговые микросхемы предназначаются для усиления, генерирования и преобразования электрических колебаний разных частот, например, для приемников, усилителей, а логические — для использования в устройствах автоматики, в приборах с цифровым отсчетом времени, в ЭВМ.

Этот практикум посвящается знакомству с устройством, принципом работы и возможным применением самых простых аналоговых и логических интегральных микросхем.

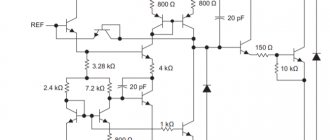

Внутреннее устройство цифровых микросхем ТТЛ

Все семейства цифровых микросхем, основываются на базовых логических элементах

. Для всех микросхем семейства ТТЛ таким элементом является

элемент 2И-НЕ

, который имеет следующее внутреннее устройство. Ниже показано схема элемента 2И-НЕ и его переходная характеристика

Схема базового элемента ТТЛ 2И-НЕ и его переходная характеристика.

На входе элемента стоит многоэмиттерный транзистор

VT1, затем

усилительный каскад

на транзисторе VT2 и

двухтактный выходной каскада

на транзисторах VT3, VT4.

Опишем работу логического элемента 2И-НЕ. В исходном состоянии входное напряжение не превышает 0,5 В, а эмиттерный переход транзистора VT1 открыт, данного напряжения не достаточно для перевода коллекторного перехода в открытое состояние, то же относится и к эмиттерным переходам транзисторов VT2, VT4. Поэтому данные транзисторы закрыты, а транзистор VT3 – открыт, напряжением, поступающим с R2. Диод VD3 оказывается открытым и на выходе элемента напряжение составляет примерно 3…4 В (точка А

). Когда начинается увеличиваться напряжение на эмиттерах VT1, то транзистор VT2 начинает открываться, а транзистор VT3 плавно закрываться (

участок А – Б

). Дальнейшее увеличение напряжения на входном транзисторе приводит к тому, что транзистор VT2 ещё больше открывается, напряжение на R3 тоже возрастает и открывается транзистор VT4. В результате, эмиттерный переход транзистора VT4 шунтирует резистор R3, и транзистор VT2 резко открывается, а напряжение на выходе элемента уменьшается. В этот момент (

участок Б – В

) все транзисторы открыты и находятся в активном режиме. Если продолжать увеличивать входное напряжение, то транзисторы VT2 и VT4 перейдут в режим насыщения (

участок В – Г

), а транзистор VT3 закроется и значение выходного напряжения станет равным напряжению насыщения транзистора VT4, а ток будет ограничен резистором R4.

Участок Б – В

переходной характеристики можно использовать

для обработки аналоговых сигналов

, в данном режиме переходная характеристика обладает высокой линейностью и максимальной потребляемой мощностью.

Внутреннее устройство цифровых микросхем КМОП

Так же как и в ТТЛ семействе, КМОП микросхемах базовым элементом является 2И-НЕ

, внутреннее устройство которого показано ниже

Схема базового элемента КМОП 2И-НЕ и его переходная характеристика.

В данном логическом элементе работают комплементарные полевые транзисторы

. Транзисторы

с каналом р-типа (VT1, VT2)

подключены к положительному проводнику источника питания,

с каналом n-типа (VT3, VT4)

соединены последовательно.

При входном напряжении 2 В и менее транзисторы VT1 и VT2 открыты, так как напряжение на участках затвор – исток (при напряжении питания 9 В) составляет не менее 7 В. Напряжение на таких же участках транзисторов VT3 и VT4 оказывается недостаточным для их открывания, поэтому на выходе элемента будет напряжение, почти равное напряжению питания, то есть около 9 В (точка А

). По мере увеличения входного напряжения транзисторы начинают открываться, а VT1 и VT2 закрываться. На

участке А – Б

этот процесс происходит сравнительно плавно, а на

участке Б – В

он ускоряется и наиболее линеен.

В точке В

транзисторы VT1 и VT2 почти полностью закрыты, а VT3 и VT4 открыты. Выходное напряжение в этом случае невелико и при дальнейшем увеличении входного напряжения до уровня источника питания оно стремиться к нулю (

точка Г

).

История

Подробнее см. Изобретение интегральной схемы

7 мая 1952 года британский радиотехник Джеффри Даммер (англ. Geoffrey Dummer) впервые выдвинул идею объединения множества стандартных электронных компонентов в монолитном кристалле полупроводника. Осуществление этих предложений в те годы не могло состояться из-за недостаточного развития технологий.

В конце 1958 года и в первой половине 1959 года в полупроводниковой промышленности состоялся прорыв. Три человека, представлявшие три частные американские корпорации, решили три фундаментальные проблемы, препятствовавшие созданию интегральных схем. Джек Килби из Texas Instruments

запатентовал принцип объединения, создал первые несовершенные прототипы ИС и довёл их до серийного производства. Курт Леговец из

Sprague Electric Company

изобрёл способ электрической изоляции компонентов, сформированных на одном кристалле полупроводника (изоляцию p-n-переходом (англ. P–n junction isolation)). Роберт Нойс из

Fairchild Semiconductor

изобрёл способ электрического соединения компонентов ИС (металлизацию алюминием) и предложил усовершенствованный вариант изоляции компонентов на базе новейшей планарной технологии Жана Эрни (англ. Jean Hoerni). 27 сентября 1960 года группа Джея Ласта (англ. Jay Last) создала на

Fairchild Semiconductor

первую работоспособную

полупроводниковую

ИС по идеям Нойса и Эрни.

Texas Instruments

, владевшая патентом на изобретение Килби, развязала против конкурентов патентную войну, завершившуюся в 1966 году мировым соглашением о перекрёстном лицензировании технологий.

Ранние логические ИС упомянутых серий строились буквально из стандартных

компонентов, размеры и конфигурации которых были заданы технологическим процессом. Схемотехники, проектировавшие логические ИС конкретного семейства, оперировали одними и теми же типовыми диодами и транзисторами. В 1961—1962 гг. парадигму проектирования сломал ведущий разработчик

Sylvania

Том Лонго, впервые использовав в одной ИС различные конфигурации транзисторов в зависимости от их функций в схеме. В конце 1962 г.

Sylvania

выпустила в продажу первое семейство разработанной Лонго транзисторно-транзисторной логики (ТТЛ) — исторически первый тип интегральной логики, сумевший надолго закрепиться на рынке. В аналоговой схемотехнике прорыв подобного уровня совершил в 1964—1965 годах разработчик операционных усилителей

Fairchild

Боб Видлар.

Первая отечественная микросхема была создана в 1961 году в ТРТИ (Таганрогском радиотехническом институте) под руководством Л. Н. Колесова[2]. Это событие привлекло внимание научной общественности страны, и ТРТИ был утверждён головным в системе минвуза по проблеме создания микроэлектронной аппаратуры высокой надёжности и автоматизации её производства. Сам же Л. Н. Колесов был назначен Председателем координационного совета по этой проблеме.

Первая в СССР гибридная толстоплёночная интегральная микросхема (серия 201 «Тропа») была разработана в 1963-65 годах в НИИ точной технологии («Ангстрем»), серийное производство с 1965 года. В разработке принимали участие специалисты НИЭМ (ныне НИИ «Аргон»)[3][4].

Первая в СССР полупроводниковая интегральная микросхема была создана на основе планарной технологии, разработанной в начале 1960 года в НИИ-35 (затем переименован в НИИ «Пульсар») коллективом, который в дальнейшем был переведён в НИИМЭ («Микрон»). Создание первой отечественной кремниевой интегральной схемы было сконцентрировано на разработке и производстве с военной приёмкой серии интегральных кремниевых схем ТС-100 (37 элементов — эквивалент схемотехнической сложности триггера, аналога американских ИС серии SN

-51 фирмы

Texas Instruments

). Образцы-прототипы и производственные образцы кремниевых интегральных схем для воспроизводства были получены из США. Работы проводились в НИИ-35 (директор Трутко) и Фрязинским полупроводниковым заводом (директор Колмогоров) по оборонному заказу для использования в автономном высотомере системы наведения баллистической ракеты. Разработка включала шесть типовых интегральных кремниевых планарных схем серии ТС-100 и с организацией опытного производства заняла в НИИ-35 три года (с 1962 по 1965 год). Ещё два года ушло на освоение заводского производства с военной приёмкой во Фрязине (1967 год)[5].

Параллельно работа по разработке интегральной схемы проводилась в центральном конструкторском бюро при Воронежском заводе полупроводниковых приборов (ныне — ОАО «НИИЭТ»). В 1965 году во время визита на ВЗПП министра электронной промышленности А. И. Шокина заводу было поручено провести научно-исследовательскую работу по созданию кремниевой монолитной схемы — НИР «Титан» (приказ министерства от 16.08.1965 г. № 92), которая была досрочно выполнена уже к концу года. Тема была успешно сдана Госкомиссии, и серия 104 микросхем диодно-транзисторной логики стала первым фиксированным достижением в области твердотельной микроэлектроники, что было отражено в приказе МЭП от 30.12.1965 г. № 403[6][7].

Логический элемент в линейном режиме

Использование логических элементов цифровых микросхем для работы с аналоговыми сигналами возможно лишь в случае, если их режим выведен в линейный

или близкий к нему. Так в линейном режиме

ТТЛ элемент

эквивалентен усилителю к коэффициентом усиления 10 … 15 (примерно 20 дБ), а

элемент КМОП

– усилителю с коэффициентом усиления 10 … 20 (20 … 26 дБ).

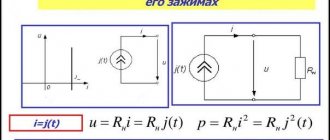

Вывод логического элемента в линейный режим: слева-направо током, напряжением, обратной связью.

Для вывода логического элемента на линейный участок применяют различные способы. Один из них основан на включении на входе элемента ТТЛ резистора R

. Этот резистор вызовет ток, который будет протекать через эмиттерный переход входного транзистора элемента ТТЛ. Изменяя сопротивление внешнего резистора, можно изменять напряжение на выходе элемента, то есть изменять положение его рабочей точки на передаточной характеристике. Для

элементов ТТЛ

сопротивление такого внешнего резистора составляет от 1 кОм до 3 кОм. Однако такой способ

не применим для КМОП микросхем

, так как они работают без выходных токов (есть токи утечки, но они малы и нестабильны).

Второй способ вывода логического элемента на рабочий режим может быть подача на вход соответствующего напряжения

, например с помощью

резистивного делителя

. Так, для

элементов ТТЛ

середина линейного участка передаточной характеристики соответствует

входное напряжение 1,5…1,8 В

, а для

КМОП 3…6 В

(при напряжении питания 9 В). Для разных логических элементов это напряжение не одинаково, поэтому его подбирают опытным путём. Номиналы входных резисторов выбирают таким образом, что бы входные токи элементов не влияли на напряжение, снимаемое с резистивного делителя.

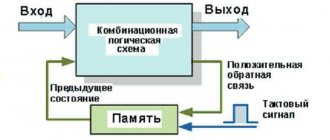

Третий способ, является наиболее эффективным, для этого создают отрицательную обратную связь (ООС)

по постоянному току между входом и выходом элемента, благодаря чему рабочая точка автоматически поддерживается на требуемом участке передаточной характеристики и не требуется тщательного подбора внешних резисторов. Этот способ реализуется для

логических элементов с инверсией

входного сигнала: НЕ, И-НЕ, ИЛИ-НЕ.

Сопротивление резистора в цепи ООС

выбирают исходя из обеспечения элементу необходимого входного тока. Для

элементов КМОП

оно составляет

от нескольких килоом до десятков мегаом

, а для

ТТЛ – от десятков Ом до 1 кОм

. Но применение ООС снижает коэффициент усиления элемента.

Усилители на логических элементах

Для использования логических элементов в качестве усилителей сигналов необходимо вывести рабочую точку на линейный участок передаточной характеристики. Основные характеристики таких усилителей приведены в таблице ниже.

| Серия | Схема вывода в линейный режим | КУС, дБ | Fmax, МГц | Рпотр мВт | Uвых, В | Rвх, кОм | Rвых, кОм | R1, кОм | R2, кОм |

| К155 | OOC | 18 | 40 | 20 | 1,2 | 0,6 | 0,05 | 0,68 | 0,68 |

| Ток | 21 | 0,8 | 1,9 | — | |||||

| К176 | ООС | 25 | 5,5 | 5 … 20 | 1,5 | 0,4 | 0,05 | 7,5 | 5,1 |

| Ток | 17 | 3 … 4 | 5,0 | 3,5 | 6 | 6,2 | 4 | ||

| 561 | OOC | 25 | 1000 | 7 | 1000 | 1000 |

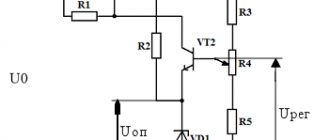

Схема простейшего усилителя на элементе ТТЛ приведена ниже. Регулировка усилителя сводится к установке подстроечным резистором R1рабочей точки элемента на середине линейного участка передаточной характеристики.

Простейший усилитель на ТТЛ элементе

Недостатком простых усилителей является невысокое входное сопротивление

, что ограничивает область их применения. К тому же коэффициент усиления небольшой. Устраняется данный недостаток использованием совместно с транзисторами. Коэффициент усиления повышается включением последовательно нескольких каскадов. Кроме того, цифровая микросхема содержит несколько идентичных элементов, это позволяет создавать многоканальные усилители. Примером может служить схема показанная ниже. Основные характеристики усилителя: коэффициент усиления – 50; выходное сопротивление 50 Ом, входное сопротивление 5 кОм, верхняя граничная частота 40 МГц.

Схема усилителя с транзистором на входе

Элементы КМОП также можно использовать для усилителей, схема одного из ни приведена ниже. Общий недостаток усилителей на элементах КМОП – высокое выходное сопротивление

. Устранить его можно установкой на выходе логического элемента

эмиттерного повторителя

на транзисторе и включения его в цепь ООС.

Схемы усилителей на элементах КМОП.

[ Содержание ]

Увлекаетесь электроникой? Приглашаем Вас принять участие в бета-тестировании онлайн-редактора электрических схем. sapr.asvcorp.ru Работайте со схемами прямо из браузера.

2.4.2 Микросхемы типа ЛА, ЛИ

Чтобы рассмотреть схемотехнику, составим таблицу функций элементов И, И-НЕ для двух входов А и В (простейший вариант). Каждая переменная А и В моделируется электронным ключом, который можно замкнуть или разомкнуть. Если ключи соединены последовательно, то они работают согласно логике И: ток в цепи появится, если замкнуть оба ключа: и А и В. Если активными входными сигналами считать замыкание ключей А и В и назвать это событие логической 1, то, последовательно перебирая состояние этих ключей, составим таблицу входных и выходных данных для элементов И и И-НЕ.

Таблица состояний

| Логический элемент | Входные переменные | Выходная функция | ||

| А | B | И | НЕ-И | |

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

Рассмотрим способ реализации логической операции И-НЕ на элементах ТТЛ. На рис. 2.8, а приведена принципиальная схема двухвходового логического элемента И-НЕ.

Рис. 2.8.а. Принципиальная схема логического элемента.

Подавая от ключей S1 и S2 на входы А и В напряжение высокого В и низкого Н уровней, составим таблицу выходных уровней элемента.

Таблица состояний логического элемета

| Вход | Выход Q(НЕ-И) | Вход | Выход Q(НЕ-И) | ||

| А | B | A | B | ||

| Н | Н | В | 0 | 0 | 1 |

| Н | В | В | 0 | 1 | 1 |

| В | Н | В | 1 | 0 | 1 |

| В | В | Н | 1 | 1 | 0 |

Напряжение низкого уровня Н появляется на выходе Q, когда на обоих входах А и В присутствует высокое напряжение В. Условное графическое обозначение двухвходового логического элемента показано на рис 2.8, в

Рис 2.8.в. Условное обозначение элемента.

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ. Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до четырех логических элементов, а микросхемы ЛА2 и ЛА19 содержат по одному логическому элементу И-НЕ на восемь и двенадцать входов соответственно.

Цоколевки микросхем типа ЛА и ЛИ и их условные графические обозначения приведены на рис. 2.9, а основные параметры даны в табл. 2.3.

Рис 2.9. Условные обозначения и цоколевки микросхем ЛИ Рис 2.9. Условные обозначения и цоколевки микросхем ЛА

Следует особо выделить группу микросхем, логические элементы которых имеют выходы с открытым коллектором (ЛА7…ЛА11, ЛА13. ЛА18), (ЛИ2, ЛИ4, ЛИ5). Схема двухвходового логического элемента И-НЕ с открытым коллектором показана на рис. 2.10, а.

Рис. 2.10а. Принципиальная схема логического элемента И-НЕ

Для формирования выходного перепада напряжения к выходу такого элемента необходимо подключить внешний нагрузочный резистор Rн. Такие микросхемы применяются для обслуживания сегментов индикаторов, зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Рис. 2.10б. Схема подключения ламп накаливания и светодиодов

При необходимости в схемах можно использовать элемент ТТЛ с двухтактным выходом. Для некоторых микросхем с открытым коллекторным выходом (ЛА11) нагрузку можно подключать к более высоковольтному источнику питания (рис. 2.10,в).

Рис. 2.10в. Схема подключения нагрузки к высоковольтному источнику

Такое включение необходимо для зажигания газоразрядных и электролюминесцентных индикаторов. Выходы с открытого коллектора используют для подключения обмоток реле.

Выходы нескольких элементов с открытым коллектором можно присоединять к общей нагрузке Rн (рис. 2.10, г).

Рис. 2.10г. Схема подключения нескольких элементов к общей нагрузке

Такое подключение позволяет реализовать логическую функцию И, называемую «монтажное И». Схему (рис. 2.10. г) используют для расширения числа входов логического элемента.

Следует помнить, что двухтактные выходы ТТЛ нельзя соединять параллельно, это приводит к токовой перегрузке одного из элементов.

Многовходовые составные логические элементы с открытым коллектором и общим сопротивлением нагрузки Rн реализуются наиболее просто, однако они не позволяют получить предельное быстродействие. Более лучший способ увеличения числа входов осуществляется с помощью специальной микросхемы-расширителя, имеющей дополнительные выводы коллектора и эмиттера фазоразделительного каскада VT2 (рис. 2.11). Одноименные вспомогательные выводы нескольких таких элементов можно объединять.

Рис. 2.11а. Принципиальная схема 2И-НЕ с дополнительными выводами коллектора и эмиттера. Рис. 2.11б. Условное обозначение расширителя и способ соединения нескольких микросхем.

Микросхема К531ЛА16 (магистральный усилитель) может передавать данные в линию с сопротивлением 50 Ом.

Микросхемы ЛА17, ЛА19 — это логические элементы И-НЕ с тремя состояниями на выходе, т. е. они имеют дополнительный вход /ЕО (Enable output), дающий разрешение по выходу. На рис. 2.12 показана схема элемента, который имеет третье выходное состояние Z, когда выход размыкается.

Рис. 2.12. Принципиальная схема логического элемента с тремя состояниями на выходе.

Для этой цели в схему стандартного сложного инвертора ТТЛ вводится дополнительный инвертор DDI и диод VD2. Если на этот вход /ЕО подать от переключателя S1 напряжение высокого уровня — 1, то выходное напряжение инвертора DD1 станет низким, т. е. катод диода VD2 будет практически соединен с корпусом. Из-за этого коллектор транзистора VT2 будет иметь нулевой потенциал, т. е. транзистор VT2 будет закрыт. Транзисторы VT3 и VT4 будут находиться в режиме отсечки, т. е. оба закрыты. Следовательно, выходной вывод как бы «висит» в воздухе, микросхема переходит в состояние Z с очень большим выходным сопротивлением. Если на вход ЕО подается разрешающий низкий уровень — О, то логический элемент И-НЕ работает как в обычном режиме.

Таблица состояний логического элемента.

| Вход | Выход | ||

| /EO | I | /Y | |

| 0 | 0 1 | 1 0 | |

| 1 | 0 1 | Z | |

Такие логические элементы разработаны специально для обслуживания проводника шины данных. Если к такому проводнику присоединить много выходов, находящихся в состоянии Z, то они не будут влиять друг на друга. Активным передающим сигналом должен быть лишь один логический элемент, только от его выхода в проводник шины данных будет поступать информация. Следовательно, соединенные вместе выходы не должны быть одновременно активными.

Чтобы сигналом разрешения (низкий уревень — О) , подаваемым на вход /EO, подключался к проводнику выход только одного логического элемента, необходимо предусмотреть дополнительный (защитный) временной интервал, т. е. переключать входы /ЕО различных элементов с паузой. Сигналы разрешения, даваемые выходам разных элементов, не должны перекрываться.

Микросхема К531ЛА19-это 12-входовый логический элемент И-НЕ с дополнительным инверсным входом /ЕО. Сигнал появится на его выходе, если на вход /ЕО подано напряжение низкого уровня — О. Выход логического элемента перейдет в разомкнутое состояние Z, если на вход /ЕО подается напряжение высокого уровня. В состоянии Z элемент потребляет ток Iпот.z=25 мА. Время задержки перехода выхода к разомкнутому состоянию tзд.1z= 16 нс, время задержки перехода выхода tзд.0z= 12 нс (от напряжения низкого выходного уровня), при условии, что Сн = 15 пФ [1].

Пороговые устройства на логических элементах

Пороговые устройства

, называемые компараторами, предназначены для преобразования аналогового сигнала в цифровую информацию. Простейшим пороговым устройством является триггер Шмитта, который описан в этом посте. Кроме формирования импульсов и восстановлении цифровых сигналов, пороговые устройства применяют в аналогово – цифровых преобразователях, генераторах импульсов различной формы.

Схема порогового устройстван на логических элементах.

По большёму счёту логический элемент является сам пороговым устройствам, однако его передаточная характеристика

не совсем линейна. Для повышения линейности передаточной характеристики логического элемента, его необходимо охватить

положительной обратной связью (ПОС)

по постоянному току через резистор R2. В таком случае он превращается в своеобразный

триггер Шмитта

с возможностью регулирования пороговых напряжений.

Ширина петли гистерезиса

(разность между пороговыми напряжениями) зависит от соотношения номиналов резисторов R1 и R2. От этих же резисторов зависит и чувствительность. При увеличении R2 и уменьшении R1 чувствительность повышается, а ширина петли гистерезиса уменьшается. Для

микросхем ТТЛ

сопротивление R1 = 0,1 … 2 кОм, а R2 = 2 … 10 кОм. Пороговые устройства на КМОП элементах отличаются высокой экономичностью, а недостатком является низкая чувствительность. Для

КМОП микросхем

R1 – несколько десятков килоом, а R2 – несколько сотен килоом.