Главная > Теория > RS триггер

Базовый строительный блок, который делает возможной компьютерную память, а также используется во многих последовательных логических устройствах является триггерной, или бистабильной, схемой. Только два взаимосвязанных логических входа составляют основную форму этой схемы, выход которой имеет два стабильных состояния. Когда схема запускается в какое-либо из них с помощью подходящего входного импульса, она будет «запоминать» это состояние до тех пор, пока оно не будет изменено дополнительным входным импульсом, или пока не отключится питание.

Логическая микросхема

Классификация последовательных схем

Последовательные схемы могут быть использованы для простых триггеров или для создания более сложных систем: устройств памяти, счетчиков, регистров сдвига. Они подразделяются на три основные категории:

- Асинхронные, меняющие статус при включении;

- Синхронные, согласованные с тактовым сигналом;

- Комбинированные, реагирующие на запуск импульсов.

Важно! Если схема зависит от внешнего входа, то она является асинхронной. Если состояния меняются в зависимости от тактового сигнала, то она синхронная. Для сохранения состояния присутствует обратная связь, когда частично сигнал с выхода идет опять на вход.

Что такое RS триггер

Хлопковый выключатель и его особенности

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

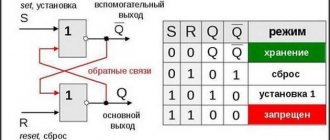

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

RS триггер

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние.

Основы электроакустики

Триггером называют логическую схему с положительной обратной связью, имеющую два устойчивых состояния – единичное и нулевое, которые обозначаются соответственно 1 и 0 (рис.23.1, а). В основе любого триггера находится кольцо из двух инверторов (рис. 23.1, б, в). Триггер является элементом памяти последовательностных логических устройств, на схемах он обозначается буквой Т

При подаче питания в результате переходных процессов произвольно один из инверторов устанавливается в единичное состояние, а другой – в нулевое. В дальнейшем состояние логических элементов (ЛЭ) сохраняется, так как сигнал с выхода одного ЛЭ поддерживает состояние другого ЛЭ. Общепринято такую схему называть элементом памяти или защелкой.

Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно.

Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации. Как правило, триггеры имеют 2 выхода: прямой и инверсный.

Рис. 23.1. Структурная схема триггера

Триггеры классифицируют по способу приема информации, принципу построения и функциональным возможностям.

По способу приема информации различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на так называемом входе синхронизации С (от англ. clock). Этот вход также обозначают терминами «строб», «такт».

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации С.

Статические триггеры воспринимают информационные сигналы при подаче на вход С логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

По способу построения различают одно- и двухступенчатые триггеры. В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом – две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ.

По функциональным возможностям триггеры разделяют на следующие классы:

- — с раздельной установкой состояния 0 и 1 (RS-триггеры);

- — универсальные (JK-триггеры);

- — с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

- — со счетным входом Т (Т-триггеры).

Входы триггеров обычно обозначают следующим образом:

- — S – вход для установки в состояние «1»;

- — R – вход для установки в состояние «0»;

- — J – вход для установки в состояние «1» в универсальном триггере;

- — К – вход для установки в состояние «0» в универсальном триггере;

- — Т – счетный (общий) вход;

- — D – вход для установки в состояние «1» или в состояние «0»;

- — V – дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

Рассмотрим некоторые типы триггеров и их реализацию на логических элементах.

Условное графическое обозначение асинхронного RS-триггера и таблица его переходов приведены на рис. 23.2.

Рис. 23.2. RS-триггер

Триггер имеет два информационных входа: S (от англ. set) и R (от англ. reset). Закон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 23.2). Через St, Rt, Qt обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt+1 выходной сигнал в следующий момент времени t+1.

Комбинацию входных сигналов St = 1, Rt = 1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций нужно избегать.

Рассматриваемый триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 23.3,а) или И-НЕ (рис.23.3,б).

Эти схемы функционируют в полном соответствии приведенной выше таблицей переходов, которая на рис. 23.2 приведена в сокращенном виде. Полная таблица истинности (таблица переходов) RS-триггера на элементах ИЛИ-НЕ имеет следующий вид (рис. 23.4).

Рис. 23.3. RS-триггер на элементах ИЛИ-НЕ (а) и И-НЕ (б)

Рис. 23.4. Таблица истинности RS-триггера на элементах ИЛИ-НЕ

В асинхронном RS-триггере на элементах И-НЕ переключение производится логическим «0», подаваемым на вход R или S, т. е. реализуется обратная рассмотренной ранее таблице переходов (рис. 23.4). Запрещенная комбинация соответствует логическим «0» на обоих входах.

Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 23.5). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье (высокоимпедансное) состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с вышеприведенной таблицей переходов.

Рис. 23.5. RS-триггер К564ТР2

Рассмотрим синхронный RS-триггер (рис. 23.6). Если на входе С – логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации. Таким образом, если на входе С – логический «0», то воздействие на входы R, S не приводит к изменению состояния триггера. Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы так же, как и рассмотренная ранее.

В рассмотренных выше RS-триггерах с обратными связями возможны неопределенности, обусловленные одновременным изменением информации на прямом и инверсном выходах, связанных с R и S входами. Для устранения этого эффекта применяются двухступенчатые триггеры.

При использовании двухступенчатого RS-триггера (рис.23.7) допускается соединение его входов и выходов. Двухступенчатый триггер состоит из двух синхронных RS-триггеров и дополнительного элемента НЕ. При подаче входных управляющих сигналов и синхросигнала (рис.23.8) производится запись информации в первый триггер (момент t1). При этом второй триггер не изменяет своего состояния, так как на его синхровход с инвертора подается логический ноль. Только по окончании записи в первый триггер при изменении синхросигнала с единицы на ноль производится запись во второй триггер двухступенчатой системы (t2).

Рис. 23.6. Синхронный RS-триггер

Рис. 23.7. Структурная схема двухступенчатого триггера

Рис. 23.8. Временная диаграмма работы двухступенчатого триггера

Таким образом, двухступенчатый триггер переключается по заднему фронту синхронизирующего импульса. Такая синхронизация называется динамической. Наличие динамической синхронизации отмечено наклонной чертой. Использование в триггере двух ступеней обозначается двумя буквами ТТ.

Рассмотрим в качестве примера RS-триггер типа 136ТР1 – синхронный триггер. Триггер имеет сложные входы R и S , вызывающие изменение состояния триггера при действии фронта синхроимпульса (перепадом с 0 на 1). Информационные входы R и S имеют входную логику «3И» (рис. 23.9).

Входы R и S (выводы 2 и 13) – установочные входы (установки 1 и 0 соответственно) действуют независимо, подан синхроимпульс или нет.

Рис. 23.9. Синхронный RS-триггер К136ТР1: а – УГО, б – таблица истинности

В таблице (рис. 23.10, б) приняты следующие обозначения:

- — любое состояние S, R-сигналов на выводах 2, 13 ИМС;

- – произведение сигналов на выводах 9, 10, 11 ИМС;

- – произведение сигналов на выводах 3, 4, 5 ИМС.

Таблица истинности

Работу триггера РС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

D – триггер

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С).

Таблица переходов D-триггера

| C | D | Q(t) | Q(t+1) | Пояснения |

| * | Режим хранения информации | |||

| * | 1 | 1 | ||

| 1 | * | Режим записи информации | ||

| 1 | 1 | * | 1 |

Если на входе D – “1”, то по приходу синхроимпульса Q = 1. Если на D “0”, то Q =0.

Временные диаграммы

Скважность импульсов

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

JK триггер

Выпрямитель тока

Другие широко распространенные виды логических схем – JK, D и Т, которые являются разработками RS триггера на логических элементах.

Недостатки схемы И-НЕ РС триггера:

- Необходимость избегать условия, когда оба входных сигнала равны 0;

- При изменениях состояния R и S, имеющих единичный входной сигнал, правильное блокирующее действие не всегда происходит.

Для преодоления этих недостатков была разработана схема JK триггера. Его входы являются теми же R и S, но им присвоены буквы J и K по имени изобретателя схемы, чтобы отличить от других триггеров. JK схема отличается от RS триггера тем, что она не имеет неопределенных или запрещенных входных статусов.

JK триггер

В JK добавлена входная схема синхронизации, предотвращающая неопределенное условие вывода, которое может случиться, если R и S равны единице. Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Перекрестная связь RS триггера позволяет использовать ранее неопределенные условия работы триггера, когда оба входных сигнала равны 1, для создания «переключателя», так как два входа могут быть блокированы.

Схема JK – это триггер SR с обратной связью, который позволяет только одному из его терминалов (SET или RESET) быть активным в любой момент времени, тем самым устраняя недопустимое условие:

- Если активен терминал SET, вход J блокируется статусом 0 (Q̃) через нижний логический элемент И-НЕ;

- Если в действии терминал RESET, вход К заблокирован статусом 0 через верхний вентиль И-НЕ.

Так как Q̃ и Q всегда разные, они могут использоваться для манипулирования входом. Для JK триггера таблица истинности принимает следующий вид.

Таблица истинности JK триггера

Когда оба входа J и K имеют единицу на входе при высоком тактовом импульсе, схема может переключаться из состояния SET в RESET и наоборот.

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна область применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Т-триггер

Триггеры типа T на логических элементах включают в себя многие возможности ранее описанных устройств. Есть модели асинхронного и синхронного типа, динамические и с дополнительным подтверждающим входом.

Асинхронные

При получении положительного сигнала на вход, на выходе получается напряжение в 2 раза выше входного. Такой эффект возможен только при импульсном сигнале, поступающем на T вход. При этом частота поступления по временной шкале не имеет препятствий, а значит сигнал доходит гораздо быстрее. Асинхронные T устройства в состоянии логической 1 на выходе имеют противофазу инверсного выхода.

Синхронные

Эти T-триггеры подобны асинхронным. Исключение состоит в наличие тактового сигнала на входе. Также существует противофаза на инверсном выходе и появление удвоенного напряжения.

Устройство T элементов можно легко отнести к делителям импульсных сигналов. Эти элементы работают только при наличии переднего фронта. Иными словами, осуществляется переход от 0 к 1. Но разница заключается в учете временного интервала между импульсами.

Триггеры типа T часто используются в логических вычислительных процессах. Осуществляется это за счет функции увеличения или снижения напряжения:

- При увеличении частоты на выходе с логической 1, осуществляется запись положительного числа.

- При уменьшении частоты на инверсном выходе при логическом 0, осуществляется запись отрицательного числа.

При учете, сколько памяти необходимо для перехода и деления сигнала, элемент может быть дополнен входом подтверждения. Программирование с использованием T-триггера допускает использование устройства в различных электронных счетчиках без встроенной памяти. Далее дана диаграмма работы устройства.