Trigger translated from English is a latch. This is an electronic module that can remain in one stable state for a long time and change it under the influence of an external signal. This is a digital automatic cell that can remember and store a binary data code of 1 bit in size. How a trigger works depends on its structure and purpose. At the heart of any such cell is a restoring ring consisting of a pair of inverters. The device contains direct and inverse outputs.

General block diagram of the latch

The place of flip-flops in digital circuitry

The PC trigger itself, as one of the structural elements in circuit design, does not contain any separate block or memory device. It is the simplest logical cell that remembers its previous and present states at the inputs and outputs. The memory is the result of the switch's operating algorithm. The device outputs are in a state of either logical zero or one. When they change, the circuit “latches” this position and remembers until the input control device, made of logical elements, gives a command to change the state.

Designation of trigger inputs

Flip-flop inputs are usually designated as follows:

S —input for setting to state “1”;

R —input for setting to state “0”;

J - input for setting to state “1” in a universal trigger;

K - input for setting to state “0” in a universal trigger;

T — counting (general) input;

D — input for setting to state “1” or state “0”;

V - additional control input to allow receiving information (sometimes the letter E is used instead of V).

Let's look at some types of triggers and their implementation on logical elements.

Classification

Before considering the operation of triggers, it is necessary to understand the designations of the inputs and outputs of such devices.

Trigger - concept and classification

The inputs (ports) of a trigger are:

- R (reset) – sets position 0, separate port;

- S (set) – sets position 1, separate port;

- J – universal latches port, sets status to 1;

- K – port of universal latches, sets status 0;

- T – counting port, changes the position of the latch.

Information. A high potential level at the input or output is equal to a logical one, a low potential level is equal to a logical zero. For TTL brand microcircuits, a logical unit is considered to be a potential from 2.4...5V, a logical zero - 0...0.4 V at a supply voltage of 5 V. For logic assemblies of other series, the potential ranges may differ.

The latch has two output ports:

- Q – straight;

- Q¯ – inverse.

When one is on the direct line (Q = 0), the “latch” is in the “1” state. In case of low potential at the output (Q = 1), the latch status is “0”.

The opposite is true for the inverse output. When output Q¯ is zero, the switch is in the one state. Position inversion is needed to implement various schematic solutions.

Attention! The types of ports determine the names of electronic switches, so, having ports R and S, it is called RS flip-flop.

A sequential logic device (PLD), which is a “latch,” is a kind of block for constructing various combinations in logical circuit circuits. The bistable state of the RS latch helps layout logic circuits such as counters, holding registers, memory devices, or shift registers. Regardless of the method of arranging logical connections, the main types of electronic switches can be divided according to the method of data input:

- synchronous type;

- asynchronous type;

- combined.

It all depends on how the control command is sent to change the state of the “latch”.

Synchronous devices

To ensure that the rs trigger does not change its position due to the combination of delayed command pulses on its ports, a synchronizing command is used. This is a clock pulse that is sent to the clock port. The changed signals at the inputs of such a “latch” will not be able to change the state at the output until a clock (synchronizing) pulse arrives. These pulses are generated by clock generators. The length of clock signals is much less than their period. Pulses determine the frequency of information replacement, linking it to discrete time periods - tl, t2,...,tn-1,tn, tn+l. This allows you to synchronize the operating processes of individual equipment units in a single rhythm.

The action of the scheme is as follows:

- if there is a zero on port C, the status of the flip-flop does not change, since information from ports S and R is not transmitted to the latch;

- if a logical one appears on port C, then the switch accepts commands from the S and R inputs and changes its position.

Such circuits have increased noise immunity, which distinguishes them favorably from asynchronous devices; the latter can turn over not only from the signal, but also from interference. The synchronous structure is used in technology related to the conversion or processing of digital data.

Synchronous RS - Trigger, Circuit and Graphic Symbol

Important! When using an RS latch with inverse inputs, it is necessary to replace the elements of the “AND” circuit with “AND - NOT” elements.

Asynchronous Models

A device that changes its state immediately when the command on the logical ports changes is called an asynchronous trigger. It contains only ports: R (reset) and S (installation). The limitations for using such circuits are associated with competition between signals, which, when they hit different inputs of the RS flip-flop, move in different ways, as if competing with each other. In this case, temporary delays and shifts occur due to various reasons: temperature changes, long service life, etc. This “race” causes frequent erroneous cell flips.

Clock synchronization in this case is not effective, therefore asynchronous cells are used as asynchronous counters, various switches, frequency dividers and similar circuit solutions.

Asynchronous RS flip-flop, block diagram

Combined schemes

A module consisting of a combination of several cells is called a combined trigger. Combinations of two or more functional cells are possible.

Table of combinations of two types of memory cells

| Device type | R.S. | R | S | E | JK | T | D | D.V. |

| R.S. | X | X | X | X | X | X | X | |

| R | X | X | X | X | X | X | ||

| S | X | X | X | X | X | |||

| E | X | X | X | X | ||||

| JK | X | X | X | |||||

| T | X | X | ||||||

| D | X | |||||||

| D.V. |

Types of triggersHere X - combining two types is possible.

The division of these devices by type can be considered using state transition tables.

The following types of state memory cells are distinguished:

- rs-latch – asynchronous and synchronous;

- jk-latch;

- d-latch;

- t-latch.

The last element of the list is a composite device, executed from a synchronous rs-memory cell.

RS triggers

Two types of such cells are considered: asynchronous and synchronous latch. Upon closer examination, a significant difference in operation and scope of application is visible.

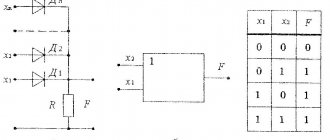

RS trigger asynchronous

The simplest type of latch, rarely used as an independent device, is a cell for constructing more complex blocks. Asynchronous cells were built on the elements:

- 2 OR – NOT, trigger cell with direct ports;

- 2 NAND, trigger cell with inverse ports.

Fixed trigger positions provide feedback. This is connecting the output of one to any input port of another logic element.

RS trigger synchronous

The basis of registers, frequency dividers and various counters is the trigger memory cell. In such devices, previously recorded information must be transferred to the output and written to the next cell using a clock pulse signal. The pulse is sent to the C-port (static or dynamic).

For your information. The static C-input synchronizes by changing the signal potential level, the dynamic C-input synchronizes the change in state not by the level, but by the moment of its change. Switching at the dynamic C-input can be carried out along the edge of the pulse (direct) or along its cut (inverse).

Consisting of a pair of synchronous RS flip-flops and an inverter, two-stage RS flip-flops are driven by a full (both edge and edge) dynamic clock pulse. Such memory cells are called master-slave (master-assistant).

JK trigger

A distinctive feature of this type of “latch” is the absence of a prohibited combination of signals on the ports. When J = K = 1, the latch position is reversed compared to the current Q0.

The JK switch differs from the RS memory cell in only one way: if “1” is applied to J and K, then it changes its position to the opposite position. An inversion occurs, and this memory cell does not have the prohibited states of the main ports.

Attention! If we draw an analogy with the designation of inputs, then J and K, respectively, are similar to the S and R inputs of an RS flip-flop. Only synchronous jk flip-flops with dynamic synchronization have found practical application.

Truth table and jk flip-flop notation

What is RS trigger

This is a memory cell capable of being in one of the stable positions: “0” or “1”. Turn over, i.e. it can change them under the influence of clock signal pulses. An elementary element assembled on two inverters cannot write or erase a stored bit. The operating principle of rs flip-flops, made on two 2I-NOT components, allows this to be done.

Universal trigger (JK trigger)

Such a trigger has information inputs J and K, which in their influence are similar to the inputs S and R of a clocked RS trigger:

- when J=1, K=0, the clock pulse trigger is set to state Q=1;

- when J= 0, K=1 – switches to state Q=0;

- when J=K=0 – stores previously received information.

But unlike a synchronous RS flip-flop, the simultaneous presence of logical 1s at the information inputs is not a prohibited combination for a JK flip-flop and leads the flip-flop to the opposite state.

JK flip-flop transition table

| K | J | C | Q(t) | Q(t+1) |

| 1 | ||||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | |||

| 1 | 1 | 1 | ||

| 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 |

Digital electronics – YB-triggers with dominant Y-input

The presence of forbidden combinations for clocked &Y flip-flops gave rise to the idea of building a trigger that forcibly sets Qx to 0 at S = 1 and R = 1 when a clock pulse is applied. This becomes possible thanks to a special connection of the inputs. In Fig. Figure 7.35 shows such a connection of inputs. When S = 1 and R = 1, the 1-signal cannot affect the flip-flop, since the output of the element is NOT 0. The AND-element is locked. 1-signal on R allows reset. The setting mode with S = 1 and R = 0 remains possible, since now the output of the NOT element is 1 and the AND element has a 1 at the output.

Interesting article: What is a solid state relay?

Such a trigger is called an .RS'-trigger with a dominant /?-input, or a ^trigger. The rule of its operation follows from the symbol in Fig. 7.36 (see also section 7.1). It says: if both inputs of the trigger S, R and input T have level 1, then with a synchronization signal 1 Q{ is set to 0, and Q2 is set to 1. The truth table of a clocked LU flip-flop with a dominant R-input is shown in Fig. 7.37. Of course, there is also a clocked RS flip-flop with a dominant ^-input (see reference test).

It will be interesting➡ Electric circuit and its elements

Truth table

D trigger - edge-controlled device and elements

The state transition table (truth table) explains the operation of an RS flip-flop using NAND elements. On it, Q 0 is the current status of the cell before the active signal hits the port. When there is no logical one at the inputs R and S, the “latch” maintains position Q 0. An active pulse R = 1 moves the latch to position 0, a pulse S = 1 to position 1. The asterisk in the table indicates the position when the combination of incoming signals is prohibited.

RS flip-flop truth table

This type has separate assignment of logical states of zero and one across information ports.

Usage

All types of triggers described above are used only in the simplest electronic control circuits. The ability of devices to synchronize and hold a signal is used in technology to interact with simple timers. A large share of use is to stabilize the operation of mechanical buttons and keys. These devices experience contact bounce. For example, when turning on electric motors. Contact bounce causes the appearance of signals with a high frequency of interaction. Triggers even out and smooth out this effect.

Simple triggers are not used in personal computers. The reason is the small operating memory capacity. The device has only a cell with a capacity of 1 bit, which is very small for complex computing technology.

Timing diagrams

Switching voltage stabilizer

In addition to truth tables, a timing diagram helps to understand the operation of a bit memory cell. In this case, the following parameters are considered on the graph when studying pulses:

- pulse duration – time interval from rise to fall;

- period – the interval from the front of the previous pulse to the front of the next one;

- duty cycle – the ratio of the pulse period to its duration.

The diagram graphically displays the signal pulses at the inputs and outputs at the same time points.

RS flip-flop timing diagram

MS type trigger

Let's consider the principle of constructing a two-stage trigger, which is also called an MS type trigger (from the English master, slave, which is usually translated as “master” and “slave”). Its simplified block diagram is shown in Fig. 3.60. The circuit has two single-stage triggers (master M and slave S) and two electronic keys (Cl1 and Cl2).

The timing diagram of the synchronization signal, explaining the operation of the trigger, is shown in Fig. 3.61.

Let's consider a number of time intervals of the indicated diagram:

t < ta — the leading trigger is disconnected from the information inputs, the slave trigger is connected to the master;

ta < t < tb — the leading trigger is disconnected from the information inputs, the slave trigger is disconnected from the master;

tb < t < tc — the master trigger is connected to the information inputs, the slave trigger is disconnected from the master. The master flip-flop records the information supplied to the inputs;

tc < t < td — the leading trigger is disconnected from the information inputs, the slave trigger is disconnected from the master;

td < t - the master trigger is disconnected from the information inputs, the slave trigger is connected to the master, information from the master trigger is rewritten to the slave. This occurs immediately after time td and means that, in fact, a two-stage flip-flop is triggered when the clock signal changes from 1 to 0. In this case, the output signals are determined by those input information signals that occurred immediately before the negative edge of the clock signal.

Classification of sequential circuits

Sequential circuits can be classified according to the following indicators:

- single-stage latches, which contain a memory element and a control device, are marked with the letter T;

- two-stage cells: static and dynamic control, used to protect against signal races, designated by the letters TT;

- switches with complex logic: single- and two-stage cells.

Single-stage cells are used as the first stages in CT switches with a dynamic control circuit and have the same control. When used independently, the controls are mostly static.

Two-stage devices have both static and dynamic control.

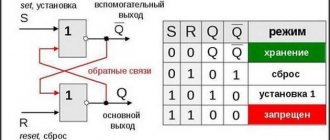

Status "Installed"

The RS switch in this state has an established circuit with Q equal to zero and Q¯ equal to one, and is independent of the controlled signal. In this case, there is a zero on R, and a logical one on S.

Status "Reset"

This is also an unchanged situation. To organize it, it is necessary to set the initial conditions. “1” is supplied to R, “0” to S. In this case, the output Q should have a value of “1”, Q¯ – the value of “0”. Feedbacks provide and fix a value independent of subsequent input values.

Metastability

The performance of flip-flops is based on the accuracy of the transition from logical parameters 1 and 0. The device is capable of operating in one state, 0 or 1. In this case, the transition from logical values is carried out without delay at a given time. The transition depends on the change in voltage at the inputs of the element.

The main problem with devices lies in the metastability effect. This is a state in which a signal reaches the input contact at the moment of transition from one state to another. At such moments, the tension is between transitions. This can lead to:

- To complete disruption of performance.

- Unauthorized switching on/off of the circuit.

- General unstable condition.

- Memory cell burnout.

Metastability can be thought of as a ball placed at the top of a hill. At the moment of transition from the logical state, the ball (voltage) moves to one of the sides according to the diagram. With metastability, the ball (voltage) slows down the transition. This effect is affected by circuit noise, high electromagnetic flux, and voltage surges.

This effect is highly dependent on the transition time interval. There is also the error of the trigger being in a state of metastability. To reduce this effect, engineers add 2 devices connected in parallel to the circuit. Such a chain makes it possible to reduce the possibility of metastability and reduce the time the chain remains in this state. Also, 2 triggers in the circuit significantly increase the transition time and reduce dependence on frequency and electromagnetic influences.

RS trigger switching diagram

The switching, setting and reset states can be viewed in the timing diagram. It is noted that the switch goes into the setting position when a zero appears at its S-input and a one at the R input, a fixed reset when a zero appears at the R port and a one at S.

Latch Switching Diagram

Attention! If zero is applied to two inputs (R and S) synchronously, then the switch, due to an uncertain state at the inputs, can flip to any unpredictable position, resulting in data corruption.

Trigger circuit modification

the rs rises , it is necessary to have at its outputs:

- during installation – Q = 1, and Q¯ = 0;

- at reset – Q = 0, and Q¯ = 1.

To organize this, the incoming latch signals are inverted. As a result, a state change is performed when positive signals are received. When modified, 2 NAND elements are added as inverters.

Trigger circuit modification

How to synchronize trigger operation

Connecting a two-port “AND” element into a serial circuit of the trigger circuit with each of the inputs will allow you to change its status, regardless of the states at the R, - or S-inputs. A new port C is obtained by combining the two ports of the “I” cells. As a result of the modification, the status at the outputs Q and Q¯ will change only when a high potential arrives at C. It is possible to connect clock generators to this new input.

Trigger Synchronization

We summarize the results in a table

We can determine the state of the Q and Q̃ signals from the following truth table:

| State | S | R | Q | Q̃ | Description |

| Installation | 1 | 0 | 0 | 1 | Output Q̃ =1 |

| 1 | 1 | 0 | 1 | without changes | |

| Reset | 0 | 1 | 1 | 0 | Output Q̃ =0 |

| 1 | 1 | 1 | 1 | without changes | |

| Invalid | 0 | 0 | 1 | 1 | error condition |

It can be seen that when S = R = 1, then Q and Q̃ can be equal to both 1 and 0 (but not at the same time!) depending on the levels of the inputs S or R before the occurrence of this output state. Thus, under the condition S = R = 1, it is impossible to change the state of the outputs Q and Q̃. It can only change when the level changes from 1 to 0 at one of the inputs.

The value S = R = 0 is an undesirable or unacceptable condition and should be avoided. The state S = R = 0 causes both outputs Q and Q̃ to be set to 1, while the state Q̃ must always be reversed Q. The result is that the flip-flop loses control of Q and Q̃, and if the two inputs now go to state 1, then the circuit becomes unstable and switches to an undefined state.

Registers on flip-flops

Since a single switch is a single-bit memory cell, to store multiple bits, the number of unit stores must be increased. A chain of such cells is called a register. The register allows you to temporarily store digital data of binary bits. The number of bits depends on the number of one-bit cells.

Circuit of a 4-bit shift register on flip-flops

The use of elementary electronic digital devices - flip-flops, allows you to create complex control circuits for logical devices. One elementary memory latch, with its bistable state, helps implement the most complex circuit designs.