What is an ADC?

Analog-to-digital converters (ADCs) are devices designed to convert analog signals into digital ones. For such a conversion, it is necessary to quantize the analog signal, i.e., limit the instantaneous values of the analog signal to certain levels, called quantization levels.

The ideal quantization characteristic has the form shown in Fig. 3.92.

Vasiliev Dmitry Petrovich

Professor of Electrical Engineering, St. Petersburg State Polytechnic University

Ask a Question

Quantization is the rounding of an analog value to the nearest quantization level, i.e., the maximum quantization error is ±0.5h (h is the quantization step).

The main characteristics of the ADC include the number of bits, conversion time, nonlinearity, etc. The number of bits is the number of bits of the code associated with the analog value that the ADC can produce.

Abrahamyan Evgeniy Pavlovich

Associate Professor, Department of Electrical Engineering, St. Petersburg State Polytechnic University

Ask a Question

People often talk about the resolution of an ADC, which is determined by the reciprocal of the maximum number of code combinations at the ADC output. Thus, a 10-bit ADC has a resolution of (210 = 1024)−1, i.e., with an ADC scale corresponding to 10V, the absolute value of the quantization step does not exceed 10mV. Conversion time tпp is the time interval from the moment of a given signal change at the ADC input until the corresponding stable code appears at its output.

Typical conversion methods are the following: parallel conversion of an analog value and serial conversion.

What is an analog-to-digital converter (ADC)?

Analog-to-digital converters (ADCs) are one of the main elements of modern data acquisition systems. Such systems consist of the following basic components:

- sensors (see the reference book “What are sensors?”);

- signal converters (see the guide “What is signal conditioning?”);

- analog-to-digital converters (ADC) (this article)

- and some kind of computer with data acquisition software that allows you to record and analyze signals.

ADCs play a large role in modern digital data acquisition systems

Main types of analog-to-digital converters

Although there are five main types of ADCs available today, in data acquisition it all comes down to two:

- successive approximation ADC and

- delta-sigma.

Other types are also quite effective, but are better suited for non-data collection applications. For example, dual ADCs operate rather slowly and are therefore mainly used in hand-held voltmeters.

Additionally, there are parallel ADCs that provide extremely high sampling rates, but their amplitude-axis resolution is too low for data acquisition needs. Pipeline ADCs rely on the use of multiple parallel converters to increase amplitude axis resolution, but their capabilities are still limited.

Comparison of the main types of ADCs

| ADC type | Advantages | Flaws | Max. permission | Max. sampling rate |

| Twin | Low cost | Low speed | 20 bit | 100 Hz |

| Parallel | Very fast | Low bit resolution | 12 bit | 10 GHz |

| Conveyor | Very fast | Limited Resolution | 16 bit | 1 GHz |

| Successive approximation (SAP) | Good ratio of speed and resolution | No internal distortion protection | 18 bit | 10 MHz |

| Delta Sigma (ΔΣ) | High dynamic performance, anti-distortion | Lag on artificial signals | 32 bits | 1 MHz |

Thus, data acquisition specialists settled on successive approximation ADCs (SAADs) and delta-sigma (ΔΣ) ADCs . Each of them has its own advantages and disadvantages and, therefore, is suitable for solving certain problems. Let's look at the operating principle of each ADC and compare them:

Example

Let's take a look at the SC9711 ADC. The operating principle of this device is complex due to its size and capabilities. By the way, speaking about the latter, it should be noted that they are truly diverse. So, for example, the frequency of possible operation ranges from 10 Hz to 10 MHz. In other words, it can take 10 million samples per second! And the device itself is not something solid, but has a modular structure. But it is used, as a rule, in complex technology, where it is necessary to work with a large number of signals.

Successive approximation ADC (SAAD)

The “workhorse” of the data processing industry is the RPP analog-to-digital converter. It provides an excellent balance of speed and resolution and processes a wide range of signals with excellent accuracy.

This converter has been around for a long time, so the RPP models are stable and reliable, and the chips are relatively inexpensive. They can be configured for both simple ADC cards, where one ADC chip is “shared” by several input channels (multiplexed ADC cards), and for models where each input channel has its own ADC for simultaneous sampling.

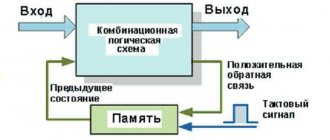

Block diagram of a typical RPP

The analog input of most ADCs is 5V, so almost all signal conditioning interfaces convert it the same way. A typical SAR ADC uses a sample-and-hold circuit that receives the converted analog voltage from the signal conditioning interface.

The on-chip processing system produces an analog reference voltage equal to the digital code output of the sample-and-hold device. Both signals are sent to the comparator, which sends the comparison result to the RPP. This process continues for n consecutive times, with n being the bit resolution of the ADC itself, until a value closest to the actual signal is found.

SAR ADCs do not have an internal filtering/smoothing mechanism, so if the data acquisition system does not provide such a component in front of the ADC, if the sampling rate is set too low, false signals (aka “noise”) will be digitized by the SAR ADC. Distortion is especially problematic because it cannot be corrected once digitized.

There is no way to fix it using software. This must be prevented by continuously sampling above the Nyquist frequency of all input signals, or by filtering the signals before and within the ADC.

For more information, see "Distortion and the Dangers of Undersampling" below.

The RPP ADC is a reliable solution for many modern data acquisition systems. They are widely used in the budget market because they can be used in multiplex mode, where multiple channels are sampled using a single ADC. They are also widely used for mid-range devices due to their speed and good amplitude axis resolution.

Due to their limited amplitude axis resolution, they are not suitable for highly dynamic measurements including noise, sound, shock and vibration, balancing, sine wave processing, etc. For such applications, delta-sigma ADCs should be considered, as discussed in the next section.

Static parameters

- Maximum

(

Vref

)

and minimum

(usually 0)

input signal levels

- set the range of the conversion scale against which the input signal will be evaluated (Fig. 1).

This parameter can also be designated as FS

- full scale. For a differential ADC, the scale is defined from -Vref to +Vref, however, for simplicity, we will further consider only single-ended scales. - Bit capacity

(

N

) is the capacity of the output code, characterizing the number of discrete values () that the converter can produce at the output (Fig. 1). - Current consumption

(

Idd

) strongly depends on the conversion frequency, so it is better to look for information about this parameter on the corresponding graph. - LSB

(

LSB

) -

Least Significant Bit

- the minimum input voltage allowed by the ADC (essentially a single step in the conversion scale). Determined by the formula: (Fig. 1). - Offset error

(

offset error

) – is defined as the deviation of the actual ADC transfer characteristic from the ideal ADC transfer characteristic at the initial point of the scale. Measured in fractions of LSB. With an offset error, the transition of the output code from 0 to 1 occurs at an input voltage different from 0.5LSB (Fig. 2).Rice.

2: Offset error There is another version of the quantizer, when the transition is carried out at integer LSB values (its characteristic will be shifted relative to the first option, which is presented in Figure 2). Both of these quantizers are equal, and for simplicity, we will further consider only the first option. - Gain Error

(

gain error

) – is defined as the deviation of the midpoint of the last conversion step (which corresponds to the input voltage Vref) of a real ADC from the midpoint of the last conversion step of an ideal ADC after offset error compensation (Fig. 3).Rice. 3: Gain error

- Differential nonlinearity

(

DNL

—

Differential nonlinearity

) is the deviation of the step width on the transfer characteristic of a real ADC from the nominal step width of an ideal converter. Due to differential nonlinearity, quantization steps have different widths (Fig. 4).Rice.

4: Differential nonlinearity For the 3-bit ADC from Figure 4: - Integral nonlinearity

(

INL

—

Integral nonlinearity

) – vertical difference between the real and ideal transformation characteristics (Fig. 5). INL can be interpreted as the sum of DNL. A negative INL indicates that the actual performance is below the ideal performance at that point on the scale. For a positive INL, the actual performance is higher than the ideal one. The DNL distribution determines the integral nonlinearity of the ADC.Rice. 5: Integral nonlinearity

- Total Unadjusted Error

(

TUE

-

Total Unadjusted Error

) is an absolute error that includes the following errors: quantization, offset, gain and nonlinearity. In other words, it is the maximum deviation between the actual and ideal conversion characteristics. For an ideal ADC, TUE = 0.5LSB, due to quantization error (or quantization noise - occurs due to rounding of the analog signal value that corresponds to the digital code). Gain and offset errors are usually the largest contributors to the absolute error. However, from a dynamic perspective (see below), offset and gain errors are negligible because they do not generate nonlinear distortion.

Delta-Sigma ADC (ΔΣ)

A newer technology is delta-sigma ADCs, which take advantage of DSP technology to improve amplitude-axis resolution and reduce the high-frequency quantization noise inherent in RPPs.

Sophisticated and powerful delta-sigma ADCs are ideal for dynamic measurements that require as much amplitude axis resolution as possible. They are used when working with sound and vibration, as well as in many advanced data acquisition systems.

Block diagram of a typical delta-sigma ADC

The DSP processor's low-pass filter virtually eliminates quantization noise, resulting in a near-ideal signal-to-noise ratio.

The implementation of these chips in data acquisition systems usually involves interface filtering and smoothing, which virtually eliminates the digitization of false signals.

When integrated at the analog interface level at the highest possible Nyquist sampling rate, and then dynamically through the DSP according to the selected sampling rate, the filtering/smoothing performance of these ADCs is simply excellent.

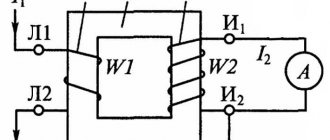

Dual Delta-Sigma ADCs - DualCoreADC®

Dewesoft also took advantage of these ADCs by combining two converters on each input channel. One ADC is set to low gain and the other is set to higher gain. Both ADCs monitor the signal simultaneously, and a proprietary circuit compares them in real time and uses the one that has the best signal-to-noise ratio at any given time, combining parallel digital signals into a continuous single stream with significantly expanded dynamic range.

DualCoreADC diagram from Dewesoft

This method greatly expands the dynamic range, which would not be possible to achieve with a single ADC. It increases dynamic range by up to a whopping 160 dB. Dewesoft has patented this technology, which is known in the market as DualCoreADC .

Video about DualCoreADC from Dewesoft

It is interesting to note that even with very slow signals, such as those from most thermocouples, the maximum possible amplitude axis resolution makes these delta-sigma ADCs preferable to RPP ADCs.

Imagine a thermocouple capable of measuring temperature over a range of 1500° - the larger the amplitude axis on the ADC, the greater the resolution of the temperature signal. Note that each bit effectively doubles the resolution of the vertical axis.

ADC in STM32F1 and operating modes

There can be several ADC modules in a microcontroller. Accordingly, they can work independently of each other (independent mode) and together (dual mode). Each module, in turn, has several channels, which are divided into regular and injected. But they are a little later. The channels themselves can be routed to the MK legs (external), or they can be connected to internal circuits (internal), for example, to the MK temperature sensor or a reference voltage source.

The STM32 microcontroller allows you to configure the conversion speed, for example 1.5, 7.5, 13.5, 28.5, 41.5, 55.5, 71.5, 239.5 ADC clock cycles. Below are macros from the standard library.

xxxxxxxxxx

#define ADC_SampleTime_1_5Cycles ((uint32_t)0x00000000)

#define ADC_SampleTime_7_5Cycles ((uint32_t)0x00000001) #define ADC_SampleTime_13_5Cycles ((uint32_t)0x00000002) #define ADC_SampleTime_28_5Cycles ((uint32_t)0x00000003) #define ADC_Samp leTime_41_5Cycles ((uint32_t)0x00000004) #define ADC_SampleTime_55_5Cycles ((uint32_t)0x00000005) #define ADC_SampleTime_71_5Cycles (( uint32_t)0x00000006) #define ADC_SampleTime_239_5Cycles ((uint32_t)0x00000007)

Since the ADC is built on capacitors, the input has a capacitive property, i.e. They need current to charge. If the input signal cannot deliver a lot of current (for example, it is removed through a voltage divider with high resistances), then it is worth choosing a longer sampling time.

All ADC operating modes are described in document AN3116.

Independent operating modes

Since there are several channels, you can work with them either one at a time or in groups. Therefore, we can distinguish single channel and multichannel. Measurements can be taken once (single conversion) or continuously (continuous). A total of 4 combinations.

- Single-channel, single conversion - one channel is used, upon completion of the conversion the result is stored in the DR register and the ADC stops. This mode is convenient to use when you need to check the supply voltage and decide to turn on the device or not.

- Single-channel continuous (English: single channel, continuous) - work is also carried out with one channel, but after saving the result to the register, the ADC restarts and makes a new measurement. This mode is convenient to use when you need to continuously monitor some parameter, for example, the battery charge level or, as in our case, the luminous flux (although in reality you can do this not so often).

- Multichannel one-time - several channels are selected, then sequentially (by serial number) the ADC makes measurements in each of them. It is worth remembering that the ADC has only one register for storing the result (DR), so the values will be overwritten.

- Multichannel continuous - works in a similar way: values are collected sequentially and after the last channel, the transformation begins all over again, from the first.

When the conversion is complete, an event occurs and a 1 is written to the corresponding bit in the Status Register (SR). The bit is reset to 0 either when the conversion result is read, or it can be reset manually. You can set up an interrupt based on an event so that the handler can somehow process the data (for example, simply save it to RAM), but this is not the most efficient way. If you have to collect a lot of data, then it is better to connect a direct memory access (DMA) module instead of interrupts, which will relieve the processor and independently copy data from the DR register to some variable or array.

As with interrupts, some system parameters may be more important than others. There is another operating mode for this.

- Injection - this mode is for transformations triggered by external events (from a timer, EXTI module or software). A group of injection channels (up to four) has priority over regular ones, so they can interrupt the operation of regular channels.

Scanning derugal and injected channels, image from AN3116

One of the channels can also be configured as an analog watchdog; its task is to monitor the voltage status on the line. If the voltage drops below the threshold, the AWD event interrupt will trigger, if configured. This is useful in cases where the device is running on battery power and you need to save/send some data before turning it off.

Collaborative mode of operation

Microcontrollers can have more than one ADC module. In some MKs from ST there can be up to three pieces. The first two can work together, but the third can only work independently. In joint mode (or paired, dual mode), the ADC1 module takes the role of the master, and ADC2 the slave. This feature is useful when you need to speed up readings.

Situations where both modules try to work with the same channel are not desirable, this may cause errors when converting the value.

- Paired, simultaneous reading of a group of regular channels (dual regular simultaneous mode, DRS) - two modules work at once, the first in the direct order of the channels, the second in the reverse.

Paired, simultaneous reading of a group of regular channels, image from AN3116

- Dual fast interleaved mode (DFI) - designed for reading one channel by both modules with a delay of 7 ADC cycles. It is possible to achieve a speed of 2 megasamples.

Paired, fast mode with overlap, image from AN3116

- Dual slow interleaved mode (DSI) - works in a similar way, but the delay between polls is 14 ADC cycles.

Paired, slow mode with overlap, image from AN3116

- Paired, alternating trigger conversion (dual alternate trigger mode, DAT) - can only work with injected channels. When a signal from the trigger arrives, one of the modules performs the conversion. When the next signal arrives, the conversion is performed by another module.

Paired, alternating trigger mode, image from AN3116

- Dual combined regular/injected simultaneous mode (DCRIS) - this mode is similar to paired reading of regular channels, with the exception that a trigger can cause the conversion of injection channels.

Paired, joint, simultaneous mode, image from AN3116

- Dual combined: injected simultaneous + interleaved mode - this mode is a combination of DFI/DSI and DCRIS modes. When a regular channel starts, pairwise interleaving begins: module ADC2 does the first conversion, then ADC1 starts, and so on. When the injection channel is started, it interrupts the overlap conversions and both modules (ADC1 and ADC2) begin converting the group of injection channels. Once the conversion is complete, the interrupted conversion resumes.

Paired, co-mode with injection, image from AN3116

ADC module registers

To complete our study of the ADC module, we need to talk about its registers. Below are all the Reference Manual for stm32f103c8 with a brief description of the bits needed in this course. However, be sure to open the documentation and study each register yourself; in other MKs they may differ (name and behavior).

The template for working with the module is approximately the following:

- enable ADC clocking (RCC);

- configure the legs for input, analog mode;

- configure the registers of the required ADC module to the desired operating mode;

- turn on the ADC;

- setting up channels;

- we start and wait for the end of calibration.

SR Status Register

- Bit 0: AWD (Analog Watchdog) flag, set to 1 if the output signal has crossed the value in the LTR / HTR registers. Reset by software.

- 1 bit: EOC (End Of Conversion) flag, set to 1 at the end of conversion (of any channel type). It is reset automatically when reading the DR register, or programmatically (by writing to the register).

- Bit 2: JEOC (Injected End Of Conversion) flag, set to 1 at the end of the conversion of a group of injection channels. Resets automatically when the DR register is read, or by software.

- Bit 3: JSTRT (Injected Start) flag, set to 1 when a group of injection channels begins conversion, reset by software.

- Bit 4: flag STRT (Start), set to 1 when a group of regular channels begins conversion, reset by software.

Settings registers CR1 and CR2

The ADC module, as you can see, is quite packed with various functionality, so the configuration register is divided into two parts. We will not describe all the bits; we will only touch on those that we need for work.

- 8 bit: SCAN (Scan mode), enables (1) or disables (0) multi-channel mode, according to the list of channels in registers SQR1, SQR2, SQR3.

- 11 bits: DISCEN (Discontinuous mode Enabled). The ADC is turned on by an external trigger.

- 13…15 bits: DISCNUM (Discontinuous mode Number of channels). Set the number of channels in sequential mode.

- 16…19 bits: DUALMOD (Dual Mode selection). Pair mode configuration.

Second settings register CR2.

- Bit 0 : ADON starts (1) or stops (0) conversion.

- 1 bit : CONT specifies single (0) or multi-channel (1) mode.

- Bit 2 : CAL calibration start register.

- Bit 3 : RSTCAL calibration reset register.

- Bit 11 : ALIGN sets whether the data is aligned to the right (0) or left (1).

- 20 bits : EXTTRIG enables or disables conversion based on a signal from a flip-flop.

Sample rate registers

The ADC_SMPR1 and ADC_SMPR2 registers set the individual conversion rate for each individual channel, each of which is allocated three bits. The following speeds are available: 1.5 (000), 7.5, 13.5, 28.5, 41.5, 55.5, 71.5, 239.5 (111) ADC tights.

What's better? RPP or delta sigma?

Each ADC technology has its own advantages. And since the applications are too different, it cannot be said that one is better than the other overall. However, it can be argued that one of them is better than the other according to a number of criteria of modern systems:

| Criterion | successive approximation ADC | Delta-Sigma (ΔΣ) ADC |

| Requires maximum amplitude axis resolution (even for slow signals such as thermocouples) | Typically 16 or 18 bits maximum | Preferable. 24-bit resolution is actually the current standard among delta-sigma boards. |

| An inexpensive multiplexed AD card must be used | The only option. It is possible to multiplex a single DPR ADC onto multiple channels to create low-cost data acquisition systems if small distortions are not critical. | N/A |

| Requires the highest possible sampling rate | Preferable. SAR ADCs are available for data acquisition at sampling rates up to 10 MS/s. | The built-in DSP limits the max. sampling rate of the delta-sigma ADC compared to the RPP ADC. |

| Filtering-smoothing is desirable | It is expensive and difficult to add successive approximation to an ADC. | Preferred because filtering/anti-aliasing is built into the delta-sigma ADC. |

| Maximum signal-to-noise ratio required | The only option. 160 dB can be achieved using Dewesoft's patented DualCoreADC® technology. | |

| Mostly artificial signals will be recorded (for example, square waves) | Reproduces square waves better. |

Read more about the different types of AD converters:

The Complete Guide to Analog-to-Digital Converters

Performance

The ADC is used for different tasks: in an oscilloscope, a high speed of signal digitization is important, but the accuracy can be neglected; In a measuring device, speed is not very important, accuracy is important. In general, the rule is this: the higher the sampling rate, the lower the measurement accuracy. For certain tasks, different topologies were invented. Here are some of them:

- Parallel, direct conversions - usually do not exceed 8 bits;

- Sequential, for example, successive approximation, or simply SAR - this is exactly what is used in the STM32F10x;

- Sigma-Delta ADCs - used in the STM32F3x series (these microcontrollers are designed more for digital signal processing tasks).

- and others.

The best tool for the job

While Dewesoft's signature solutions are its 24-bit delta-sigma ADCs and DualCoreADC technology, the company also uses 16-bit SAR ADCs to achieve a maximum sample rate of 1 MS/s in its line of SIRIUS data acquisition systems.

These include high-speed signal converters SIRIUS HS. Standard and HD Series signal converters use 24-bit delta-sigma ADCs.

SIRIUS HS signal conditioners provide powerful filtering and smoothing in the form of 100 kHz 5th order filtering . In the digital domain, an additional filter is provided (Bessel, Butterworth (or bypass) to choose from) up to the 8th order.

Powerful filtering and anti-aliasing is built into all Dewesoft 24-bit ADC signal converters.

Explore Dewesoft Data Acquisition Systems with Advanced Signal Conditioning

ADC bandwidth and subsampling (undersamling/sub-sampling)

Converter bandwidth

(

FPBW

-

Full Power (Analog) Bandwidth

). Typically the converter bandwidth is several Nyquist zones. This parameter should be in the specification, but if it is not, you can try to independently estimate the minimum possible bandwidth for a given ADC. During the sampling period, the UVH capacitance must be charged with an accuracy of 1 LSB. If the sampling period is , then the sampling error of the full scale signal is equal to: Solving for t, we obtain: Assuming that , we determine the minimum ADC bandwidth (for ): For example, for a 16-bit ADC with a sampling rate of 80 MSa/s and a scale of 2 V, the lower limit for the bandwidth calculated using this formula will be FPBW = 282 MHz.

Analog Bandwidth is a very important parameter when building systems that operate in subsampling mode. Let's explain this in more detail. According to the Nyquist criterion, the spectrum width of the processed signal must be at least 2 times less than the sampling frequency to avoid aliasing. What is important here is that it is the bandwidth, and not just the maximum frequency of the signal. For example, a signal whose spectrum is located entirely in the 6th Nyquist zone can theoretically be sampled without loss of information (Fig. 11). By limiting the spectrum of this signal with an anti-aliasing filter, it can be fed to a sampler with a frequency of fs. As a result, the signal will be reflected in each zone.

Rice.

11: undersampling Spectrum transfer property during sampling

Undersampling or sub-sampling occurs due to the properties of sampling. Let's consider an example, let there be a signal a(t) and its spectral density (Fig. 12). It is necessary to find the spectral density of the signal after sampling the signal.

Fig. 12: sampling of a continuous signal

Based on the filtering property of the delta function:

After sampling: where

Using the Rayleigh formula, we calculate the spectrum:

From this expression it follows that the signal spectrum will be repeated in all Nyquist zones. So, if you have a good anti-aliasing filter, then by observing the Nyquist criterion, you can digitize a signal with a sampling frequency much lower than the ADC bandwidth. But downsampling must be used carefully. It should be taken into account that the dynamic parameters of the ADC degrade (sometimes very strongly) with increasing frequency of the input signal, therefore it will not be possible to digitize a signal from the 6th zone as “purely” as from the 1st. Despite this, subsampling is actively used. For example, for processing narrowband signals, when you don’t want to spend money on an expensive broadband high-speed ADC, which in addition has high consumption. Another example is IF sampling in RF systems. There, thanks to undersampling, it is possible to exclude from the radio receiving path an extra analog link - a mixer (which transfers the signal to a lower carrier or to 0).

Multiplexing or one ADC per channel

Very often, low-cost data acquisition systems such as data loggers or industrial control systems use multiplexed ADC cards because they are cheaper than implementing separate ADC chips for each input channel.

In a multiplex ADC system, a single analog-to-digital converter is used to convert multiple signals from analog to digital form. This is accomplished by multiplexing the analog signals into the ADC one at a time.

This is a more cost-effective approach, but it is not possible to accurately align signals on the time axis because only one signal can be converted at a time. Therefore, there is always a time skew between channels. If slight distortion is not critical in a given application, then this is not necessarily a bad thing. The same applies to analog devices used in the system: choosing the optimal solution, taking into account functionality and service life, is important.

In addition, since the maximum sampling rate is always divided by the number of channels being read, the maximum sampling rate per channel is usually lower in multiplex systems unless only one or a small number of channels are being sensed.

When it comes to modern data acquisition systems, multiplex ADCs are used primarily in low-end applications where cost is more important than accuracy or speed.

Introduction

I would like to start with an interesting philosophical question: if an analog signal is infinity, do we lose an infinite amount of information when digitizing the signal? If this is true, then what is the point of such an ineffective transformation? In order to answer this question, let's understand what analog-to-digital signal conversion is. The main graph that reflects the operation of the ADC is the conversion transfer characteristic. In an ideal world, this would be a straight line, meaning that each analog signal level would have a single digital equivalent.

Rice.

1: Ideal ADC performance However, due to the presence of various types of noise, we cannot increase the ADC bit capacity indefinitely. That is, there is a limit that limits the minimum price of the scale division. In other words, by decreasing the scale division, sooner or later we will “run into” noise. Yes, of course, you can make at least a 100-bit ADC, but most of the bits of this ADC will not carry useful information. That is why the ADC characteristic has a step form, which is equivalent to the presence of a finite bit capacity of the ADC. When designing a system, it is necessary to select an ADC that would ensure no loss of information during digitization. In order to choose a converter, you need to understand what parameters characterize it. ADC parameters can be divided into 2 groups:

- Static

- characterize the ADC with a constant or very slowly changing input signal. These parameters include: the maximum and minimum permissible value of the input signal, bit depth, integral and differential nonlinearity, temperature instability of conversion parameters, etc. - Dynamic

- determine the maximum conversion speed, the maximum frequency of the input signal, noise and nonlinearity.

What is sampling rate?

The speed at which signals are converted is called the sampling rate. Some applications, such as most temperature measurements, do not require high speed because the signals do not change very quickly.

However, AC voltage and current analysis, shock and vibration analysis, and many other applications require sampling rates of tens or hundreds of thousands of samples per second or more. The sampling rate is usually called the T (or X) axis of measurement.

Analog signal recorded by ADC

Dewesoft offers data acquisition systems with maximum sampling rates as shown below:

| Model | Option | Interface | Max. sampling rate (per channel) |

| SIRIUS | Dual Core | USB | 200 ksa/s |

| SIRIUS MINI | Dual Core | USB | 200 ksa/s |

| SIRIUS | Dual Core | EtherCAT | 20 ksa/s |

| SIRIUS | HD (high density) | USB | 200 ksa/s |

| SIRIUS | HD (high density) | EtherCAT | 10 ksa/s |

| SIRIUS | HS (high speed) | USB | 1 MSa/s |

| DEWE-43A | Standard | USB | 200 ksa/s |

| KRYPTON | Multichannel | EtherCAT | 20 ksa/s |

| KRYPTON | Single channel | EtherCAT | 40 ksa/s |

| IOLITE | Standard | EtherCAT | 20 ksa/s |

Distortion and the dangers of undersampling

Understanding the nature of signals and their maximum possible frequencies is an important part of accurate measurements. Let's say we want to measure the output of an accelerometer.

If we expect it to oscillate at a maximum frequency of 100 Hz, we should set the sampling rate to at least twice that (Nyquist principle). In practice, to obtain a high-quality signal, it is better to set the sampling frequency 10 times higher. So in this case we set the sampling rate to 1000 Hz and take the measurement.

Theoretically, everything is as it should be, but what if the signal frequency does not increase at high amplitude? If this is the case, then our system will not be able to accurately measure or convert the signal. In addition, the measured values may be completely incorrect.

To get an idea of the distortion caused by undersampling, watch an old movie about a passing carriage when cameras were still shooting at 24 frames per second: at different speeds, it can look like the wheels are spinning backwards or not moving at all.

It is a kind of stroboscopic visual effect caused by the harmonic relationship between the speed of the wheel and the shooting speed of the camera. You may have come across videos where it seems like a helicopter is hanging in the air, but its blades are not moving at all. This occurs if the camera's shutter speed was synchronized with the speed of rotation of the helicopter blades.

This is unimportant for cinematography, but if we are doing science, it is impossible for us to seriously believe that the wheels of a car rotate backwards, and the rapidly rotating blades of a helicopter do not move.

In terms of digitizing voltage signals using an ADC, it is important that the sampling rate is set appropriately. If we set the value too high, we will waste processing power and end up with data files that are too large and unreadable. Too low a sampling rate, in turn, creates two problems:

- loss of important components of the dynamic signal;

- receiving false (distorted) signals (if the system does not have filtering-smoothing).

A clear example of a sample rate that is too low: the original signal and the result (in black) is a false signal (noise).

Preventing Distortion

Dewesoft solutions prevent distortion by using 24-bit ADCs with built-in anti-aliasing filters. These filters work in several stages. One step involves automatically tuning to the Nyquist frequency (usually around 40%) of the selected sampling rate. This way, even if you choose a sampling rate that is too low, spurious or “garbled” signals will not ruin the measurement.

Dynamic parameters

- Sampling frequency

(

fs

—

sampling frequency

) is the frequency at which the conversion to the ADC occurs (well, or 1/Ts, where Ts is the sampling period). Measured in the number of samples per second. Typically, this designation refers to the maximum sampling frequency at which the converter parameters are specified (Fig. 6).Rice. 6: ADC conversion process

- Signal to noise ratio

(

SNR

—

Signal-to-Noise Ratio

) - defined as the ratio of the power of the processed signal to the power of noise added during the conversion process. SNR is usually expressed in decibels (dB) and is calculated using the following formula: This expression is clearly demonstrated in Figure 7.Rice.

7: Signal to Noise Ratio To estimate the SNR of an ADC during system design, you can use the following formula:The first 2 terms take into account the signal level and quantization error (you need to understand that the formula is correct for the full scale signal).

The third term takes into account the effect of oversampling (processing gain )

: if the bandwidth of the signal being processed (BW < fs/2), then by applying a digital low-pass filter (or a bandpass filter, everything depends on the bandwidth and carrier) to the conversion result, you can cut out some of the ADC noise, and the remaining part will be distributed from 0 to BW (Fig. 8). If the ADC noise is uniformly distributed over all frequencies (the so-called “white” noise), the integral noise after filtering will decrease by fs/2 / BW times, which is reflected by the third term of the formula.Rice. 8: Increasing SNR due to oversampling

- General nonlinear distortion

(

THD

—

total harmonic distortion

). Before the signal is converted to digital code, it passes through nonlinear blocks that distort the signal. For example, let there be a signal with frequency f. After passing through the nonlinear block, components with frequencies 2f, 3f, 4f ... will be added to it - 2nd, 3rd, 4th, etc. harmonics of the input signal. If the sampled signal is decomposed into a spectrum using the DFT (Discrete Fourier Transform), we will see that all these harmonics are “transported” to the first Nyquist zone (from 0 to fs/2) (Fig. 9).Rice.

9: Harmonic Distortion Spurious harmonics distort the processed signal, which degrades system performance. This effect can be measured using the total harmonic distortion characteristic. THD is defined as the ratio of the total power of harmonic frequency components to the power of the fundamental (original) frequency component (expressed in dB in some documentation): - Harmonic-free dynamic range

(

SFDR

-

Spurious-Free Dynamic Range

). It is the ratio of the power of the useful signal to the power of the largest “spur” (any spurious component in the spectrum, not necessarily of harmonic origin) present in the spectrum (Fig. 9). - Signal-to-noise and nonlinear distortion ratio

(

SINAD

- signal-to-noise and distortion ratio).

Similar to SNR, but in addition to noise, it takes into account all types of interference and distortion that occur during analog-to-digital conversion. SINAD is one of the key parameters characterizing the ADC (in some sources referred to as SNDR

): - Effective number of bits

(

ENOB

-

effective number of bits

) is a kind of abstract characteristic that shows how many bits in the ADC output code actually carry useful information. Can take fractional values. - Intermodulation distortion

(

IMD

—

intermodulation distortion

). The dynamic parameters discussed earlier are measured when a single-tone harmonic signal is applied to the input. These single-tone tests are good when the ADC is processing wideband signals. In this case, harmonics located above fs/2 are reflected into the first Nyquist zone and, therefore, are always taken into account in the calculation of parameters. However, when dealing with narrowband signals or oversampling ADCs, even low-order harmonics (2nd, 3rd) may have a frequency high enough to fall outside the frequency range in question (or not be reflected into this range in the case of going beyond fs/ 2). In this case, these harmonics will not be taken into account, which will lead to an erroneous overestimation of the dynamic parameters. To solve this problem, biharmonic tests are used. Two spectrally pure sinusoids of equal power with frequencies and , which are located at a close distance from each other, are supplied to the input. The nonlinearity of the converter generates additional tones in the spectrum (they are called intermodulation distortions) at frequencies , where are arbitrary integers. The usefulness of the biharmonic test is that some of the intermodulation products lie very close to the original signal in the spectrum and therefore provide complete information about the nonlinearity of the ADC. In particular, 3rd order intermodulation distortion is found at frequencies and (Fig. 10).Rice.

10: intermodulation distortion When building RF systems, 2nd and higher order products may also be of interest. The ADC parameter, characterizing its intermodulation distortion of the nth order, is determined by the formula: [dBc], where is the power of identical sinusoids at the input, is the power of one of the products. For example, the ratio of power on to power on

What is bit resolution and why is it important?

In the early days of data acquisition, 8-bit ADCs were common. As of this writing, 24-bit ADCs are the standard for most data acquisition systems designed to make dynamic measurements, and 16-bit is considered the minimum resolution for signals in general. There are a number of low-cost systems that use 12-bit ADCs.

Since each bit of resolution effectively doubles the conversion resolution, systems with 24-bit ADCs provide 2^24 = 16,777,216. Thus, the single-voltage input signal can be divided into more than 16 million Y-steps.

The 16,777,216 steps for a 24-bit ADC are significantly better than the maximum theoretical 65,656 steps for a 16-bit ADC. Thus, the higher the resolution, the better the shape and accuracy of the wave functions. The same applies to the time axis.

Compare 24-bit resolution (orange) and 16-bit resolution (gray)

DualCoreADC® Technology and Why It's Important

One of the long-standing engineering problems with the amplitude axis is dynamic range. For example: what if we have a signal that is usually less than 5 volts, but can sometimes fluctuate upward sharply? If we set the ADC resolution to 0-5V, the system will be completely overloaded if the signal exceeds this level.

One solution would be to have two channels set to different gains; and send 0–5 V data to one of them, and with a higher amplitude to the other. But this is very inefficient: we cannot use two channels for each input signal - this will reduce the performance of the data acquisition system by half. Data analysis after each measurement will also become more complicated and time-consuming.

DualCoreADC® technology solves this problem by using two separate 24-bit ADCs per channel and automatically switching between them in real time to create a single, continuous channel. These two ADCs always measure the high and low gain of the input signal. This ensures full measurement of the sensor range and prevents signal clipping.

Video explaining Dewesoft's DualCoreADC technology

With DualCoreADC® technology, SIRIUS data acquisition systems achieve 130 dB signal-to-noise ratio and over 160 dB dynamic range. This is 20 times better than typical 24-bit systems can provide.

List of previously published chapters

- Method of direct input matching of the ADC PP (SAR) without a buffer amplifier

- Measurements using low power sensors: 12-bit single-ended design with dual 3.3V power supplies at 1 ksps

- Measurements using low power sensors: 12-bit, single-ended circuit with single 3.3 V power supply, 1 ksps

- High Voltage Battery Monitoring Circuit Based on 18-Bit Differential ADC

- Single-ended to differential signal converter circuit using a differential amplifier

- True Differential Attenuator Circuit for Analog Input Block with High Impedance Input for SAR ADC

- Input voltage range expansion circuit on the built-in analog front end (AFE) SAR ADC

Translated by Alexander Rusu at the request of COMPEL JSC

•••